在现代电子设备中,印制电路板(PCB)作为电子元器件的载体和连接枢纽,其设计质量直接影响产品的性能和可靠性。叠层设计作为PCB设计的关键环节,需要遵循一系列基本原则才能确保电路板的信号完整性、电源完整性和电磁兼容性。合理的叠层设计不仅能提高产品性能,还能降低生产成本,缩短开发周期。

叠层结构选择依据

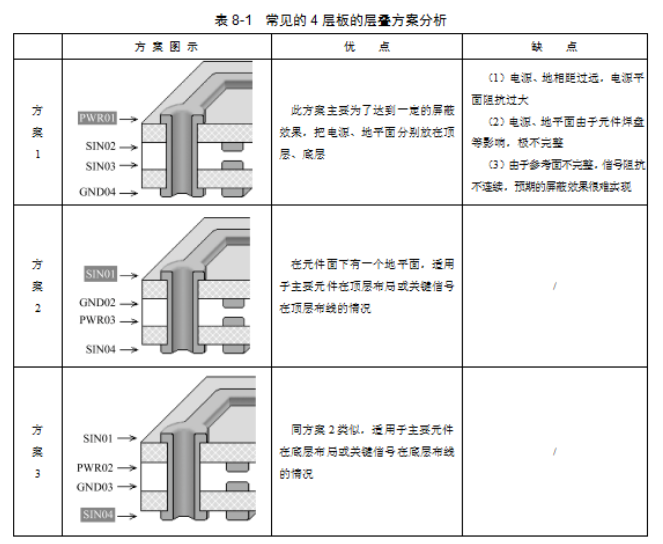

叠层结构的确定需要综合考虑电路板的用途、工作频率、信号类型和成本要求。对于低频数字电路和简单模拟电路,四层板结构通常就能满足要求。这种结构包含两个信号层、一个电源层和一个地层,在成本和性能之间取得了良好平衡。当电路工作频率超过100MHz或涉及高速数字信号时,需要考虑六层或八层板结构,为关键信号提供完整的参考平面。

高频电路和高速数字电路通常需要更多层数,以便为敏感信号提供足够的隔离和完整的回流路径。射频电路对叠层设计有特殊要求,可能需要采用特殊的介质材料和控制阻抗的严格公差。混合信号电路需要特别注意数字和模拟部分的隔离,通常要求独立的电源和地层。

电源与地平面布置

电源和地平面的布置对PCB性能有决定性影响。理想情况下,每个电源平面都应该有对应的地平面相邻布置,形成耦合电容,这对高频噪声的抑制至关重要。核心电源如CPU核心电压应该靠近器件放置,减少供电回路阻抗。多个电源电压共存时,需要考虑电源分割的合理性,避免形成狭长的分割区域产生天线效应。

地平面应尽量保持完整,避免过多分割。关键信号层应该与地平面相邻,这样可以为高速信号提供明确的回流路径。对于多层板,建议采用对称的叠层结构,这有助于减少板件翘曲。电源和地平面之间的介质厚度也需要仔细考量,太厚会增加电源阻抗,太薄则可能增加制造成本。

信号层安排策略

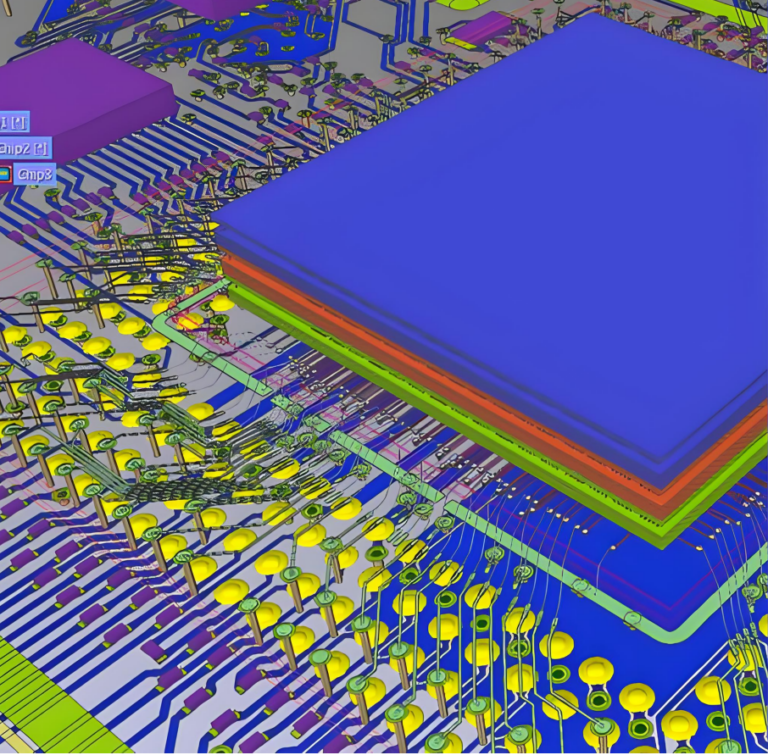

信号层的安排需要考虑信号类型、传输速率和敏感度。高速信号应该布置在内层,介于两个参考平面之间,这样可以得到最好的电磁屏蔽效果。时钟等关键信号应该与地平面相邻,并远离其他活跃信号线。不同速率的信号应该分层布置,高速信号和低速信号尽量避免同层走线。

敏感模拟信号应该与数字信号分层布置,必要时采用隔离带进行隔离。对于差分信号,应该保持线对在同一层走线,避免不必要的过孔和层间转换。布线密集的区域可以考虑增加信号层,但要注意保持对称的叠层结构。信号层与参考平面之间的介质厚度会影响特性阻抗,需要根据阻抗要求精确计算。

介质材料选择要点

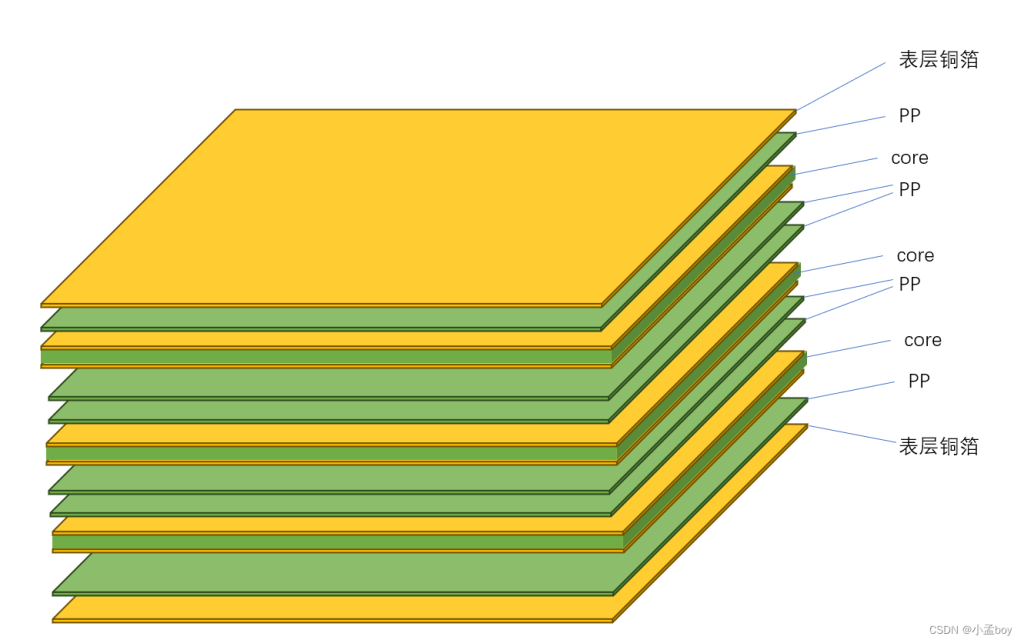

介质材料的选择直接影响PCB的电气性能和可靠性。常规FR-4材料适用于大多数低频和中等频率应用。高频电路需要考虑低损耗材料如Rogers或Taconic,这些材料具有更稳定的介电常数和更低的损耗角正切。多层板的芯板和半固化片需要匹配热膨胀系数,避免层压后产生应力。

介质厚度需要根据阻抗控制和电源去耦需求进行选择。较薄的介质有利于提高层间耦合,但会增加制造成本和降低可靠性。高电压应用需要确保足够的介质厚度以满足安全间距要求。特殊环境如高温或高湿度应用可能需要选择特种材料。材料的玻璃化转变温度应该高于PCB的最高工作温度。

阻抗控制设计方法

阻抗控制是高速PCB设计的核心要求。设计前需要明确各信号的阻抗要求,常见的有单端50欧姆和差分100欧姆。微带线和带状线的阻抗计算公式不同,需要根据叠层结构正确选择。介质厚度、线宽和铜厚是影响阻抗的三个主要因素,设计时需要综合考虑。

阻抗计算应该考虑实际生产工艺能力,留有适当余量。不同层的阻抗可能需要分别计算,因为介质厚度可能不同。阻抗不连续点如过孔、连接器等需要特别处理,尽量减少阻抗突变。关键网络应该进行三维场仿真验证阻抗连续性。批量生产前必须进行阻抗测试确认,通常允许±10%的偏差。

过孔设计注意事项

过孔设计直接影响多层板的可靠性和信号质量。过孔尺寸应该与板厚成比例,避免高厚径比增加电镀难度。高速信号的过孔应该尽量少,必要时采用盲埋孔技术减少stub效应。电源和地过孔应该足够多,降低平面阻抗。

过孔与走线的连接处应该平滑过渡,避免尖锐角度。密集过孔区域需要注意保持足够的间距,防止钻孔破裂。高频信号的过孔可能需要采用背钻技术去除无用孔段。关键信号的过孔可以添加接地过孔提供屏蔽。过孔阻焊设计要确保良好的焊接可靠性。

热管理考虑因素

叠层设计需要兼顾电路板的热性能。大功率器件下方的铜层可以适当加厚或增加导热过孔。电源平面分割时要考虑电流分布和热分布均匀性。多层板可以通过合理布置铜层形成导热路径。

高温区域的介质材料应该选择较高玻璃化转变温度的产品。不对称的叠层结构可能导致板件受热翘曲,需要避免。必要时可以预留散热金属层或考虑嵌入散热片的设计。高密度组装板可能需要增加内部散热通道。

制造工艺约束

叠层设计必须考虑实际生产工艺能力。层间对准精度限制了最小线宽和间距的选择。铜厚选择需要考虑电流承载能力和蚀刻精度要求。层压顺序和压力参数影响最终介质厚度,设计时需预留余量。

特殊结构如盲埋孔会增加工艺复杂度和成本,应该合理使用。阻抗控制要求严格的板件需要选择工艺稳定的供应商。设计前应该与制造商确认具体的工艺能力和材料库存。叠层结构应该尽量简化,在满足性能要求的前提下减少层数。

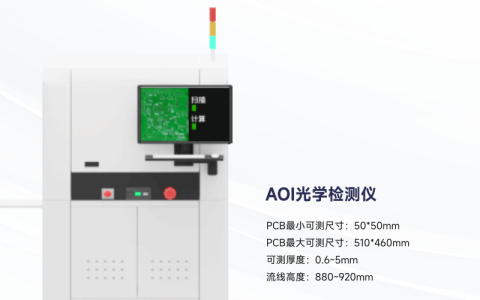

测试与验证要求

叠层设计完成后需要进行全面验证。阻抗测试应该覆盖所有关键网络和层别。电源完整性测试需要验证各种工作模式下的噪声水平。必要时进行热成像测试确认温度分布符合预期。

高速信号需要进行眼图或时域反射测试验证信号质量。批量生产前应该制作原型板进行功能和环境可靠性测试。测试结果应该反馈到叠层设计中进行优化迭代。建立完整的叠层设计规范文档,供后续项目参考。

良好的PCB叠层设计需要在电气性能、热性能、机械可靠性和制造成本之间取得平衡。设计者应该充分理解各种设计原则背后的物理意义,根据具体应用场景灵活应用。随着设计工具和制造工艺的进步,叠层设计的方法也在不断发展,但上述基本原则仍然是保证PCB设计质量的基石。通过系统化的叠层设计和严格的验证流程,可以大大提高电子产品的性能和可靠性。

转载请注明出处:PCB叠层设计原则 https://www.yhzz.com.cn/a/25902.html

免责声明:文章内容来自互联网,本站仅作为分享,不对其真实性负责,如有侵权等情况,请与本站联系删除。

转载请注明出处:PCB叠层设计原则 https://www.dachanpin.com/a/elec/33408.html